- 您现在的位置:买卖IC网 > Sheet目录313 > AT88SC12816C-MJ (Atmel)IC EEPROM 128KBIT 1.5MHZ M2J

AT88SC12816C

1.2.

Embedded Applications

Through dynamic and symmetric mutual authentication, data encryption, and the use of encrypted checksums, the

AT88SC12816C provides a secure place for storage of sensitive information within a system. With its tamper detection

circuits, this information remains safe even under attack. A 2-wire serial interface running at 1.0 MHz is used for fast

and efficient communications with up to 15 devices that may be individually addressed. The AT88SC12816C is

available in industry standard 8-lead packages with the same familiar pinout as 2-wire serial EEPROMs.

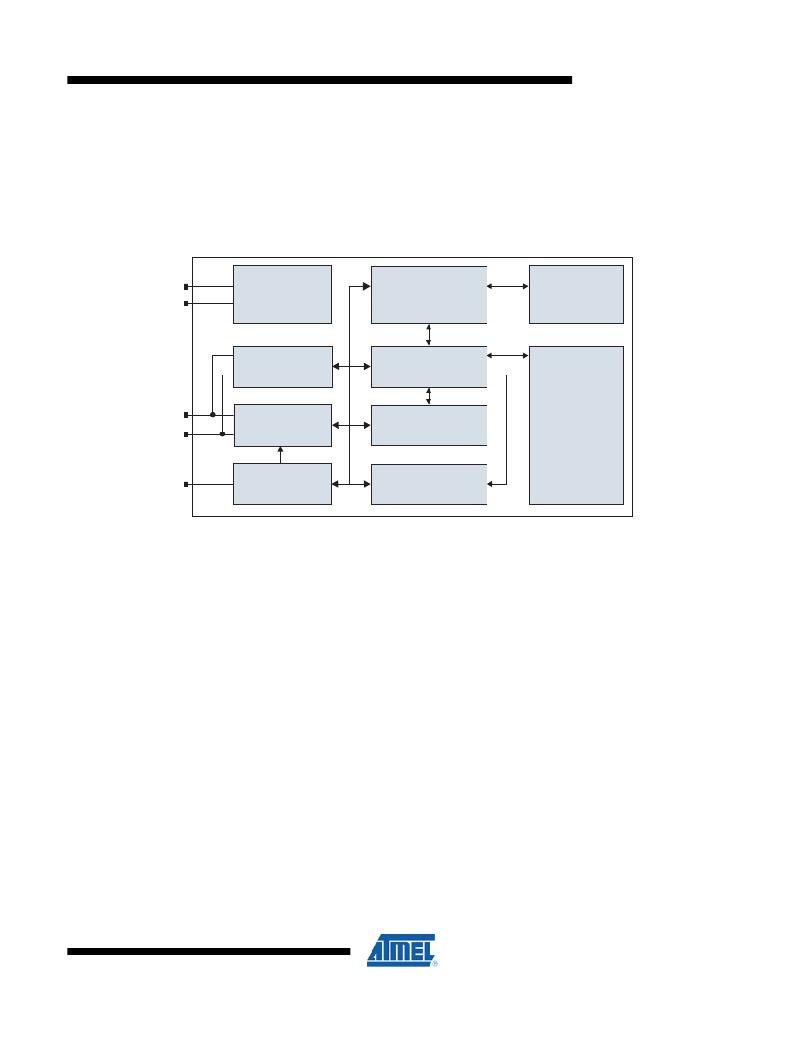

Figure 2.

Block Diagram

V CC

GND

SCL/CLK

SDA/IO

RST

Power

Management

Synchronous

Interface

Asynchronous

ISO Interface

Reset Block

Authentication,

Encryption and

Certification Unit

Data Transfer

Password

Verification

Answer to Reset

Random

Generator

EEPROM

2.

2.1.

2.2.

2.3.

Pin Descriptions

Supply Voltage (V CC )

The V CC input is a 2.7V to 5.5V positive voltage supplied by the host.

Clock (SCL/CLK)

In the asynchronous T = 0 protocol, the SCL/CLK input is used to provide the device with a carrier frequency f . The

nominal length of one bit emitted on I/O is defined as an “elementary time unit” (ETU) and is equal to 372/ f . When the

synchronous protocol is used, the SCL/CLK input is used to positive edge clock data into the device and negative edge

clock data out of the device.

Reset (RST)

The AT88SC12816C provides an ISO 7816-3 compliant asynchronous answer to reset sequence. When the reset

sequence is activated, the device will output the data programmed into the 64-bit answer-to-reset register. An internal

pull-up on the RST input pad allows the device to be used in synchronous mode without bonding RST. The

AT88SC12816C does not support the synchronous answer-to-reset sequence.

3

5016KS–SMEM–08/09

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

AT88SC25616C-MJ

IC EEPROM 256BIT 1.5MHZ M2J

AT88SC3216C-MJ

IC EEPROM 32KBIT 1.5MHZ M2J

AT88SC6416C-MJ

IC EEPROM 64KBIT 1.5MHZ M2J

AT91EB40A

KIT EVAL FOR ARM AT91R40008

AT91EB42

KIT EVAL FOR ARM AT91M42800A

AT91EB55

KIT EVAL FOR ARM AT91M55800A

AT91SAM-ICE

EMULATOR FOR AT91 ARM7/ARM9

AT91SAM7A3-EK

KIT EVAL FOR AT91SAM7A3

相关代理商/技术参数

AT88SC12816C-MJTG

功能描述:电可擦除可编程只读存储器 CRYPTOMEMORY,128KBIT 16 ZONE RoHS:否 制造商:Atmel 存储容量:2 Kbit 组织:256 B x 8 数据保留:100 yr 最大时钟频率:1000 KHz 最大工作电流:6 uA 工作电源电压:1.7 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-8

AT88SC12816C-MP

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:CryptoMemory 128 Kbit

AT88SC12816C-PI

功能描述:电可擦除可编程只读存储器 128k bit RoHS:否 制造商:Atmel 存储容量:2 Kbit 组织:256 B x 8 数据保留:100 yr 最大时钟频率:1000 KHz 最大工作电流:6 uA 工作电源电压:1.7 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-8

AT88SC12816C-PU

功能描述:电可擦除可编程只读存储器 CRYPTOMEMORY 128kB 16 ZONE - 8 IND TEMP RoHS:否 制造商:Atmel 存储容量:2 Kbit 组织:256 B x 8 数据保留:100 yr 最大时钟频率:1000 KHz 最大工作电流:6 uA 工作电源电压:1.7 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-8

AT88SC12816C-SI

功能描述:电可擦除可编程只读存储器 128k bit RoHS:否 制造商:Atmel 存储容量:2 Kbit 组织:256 B x 8 数据保留:100 yr 最大时钟频率:1000 KHz 最大工作电流:6 uA 工作电源电压:1.7 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-8

AT88SC12816C-SU

功能描述:电可擦除可编程只读存储器 CRYPTOMEMORY 128kB 16 ZONE - 8 IND TEMP RoHS:否 制造商:Atmel 存储容量:2 Kbit 组织:256 B x 8 数据保留:100 yr 最大时钟频率:1000 KHz 最大工作电流:6 uA 工作电源电压:1.7 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-8

AT88SC12816C-SU SL383

制造商:Atmel Corporation 功能描述:EEPROM Serial-2Wire 128K-Bit 8K x 16 3.3V/5V 8-Pin SOIC

AT88SC12816C-WI

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:CryptoMemory 128 Kbit